XILINX 时序约束使用指南笔记 ——时序约束介绍 时序约束方法 时序约束原则等

”fpga时序教程 xilinx_约束 时序分析 时序约束 约束“ 的搜索结果

xilinx公司提供的关于FPGA硬件设计的额时序约束参考资料

时序例外在之前的文章中讲过,如果不去约束的话,可能会造成时序资源的浪费,不因该分析的分析了,不应该优化的优化了,不应该这么严格去分析的也这么严格的去分析了,跑这样的程序浪费电脑资源,同样也会增加运行...

时序约束中的set_max_delay和set_min_delay的详解

主时钟通常是FPGA器件外部的板级时钟(如晶振、数据传输的同步时钟等)或FPGA的高速收发器输出数据的同步恢复时钟信号等。

前三章我们已经掌握了时序分析基本原理。但是,综合工具不知道我们的设计时钟频率是多大,我们想要的...设计者根据实际的系统功能,通过时序约束的方式提出时序要求FPGA 编译工具根据设计者的时序要求,进行布局布线。

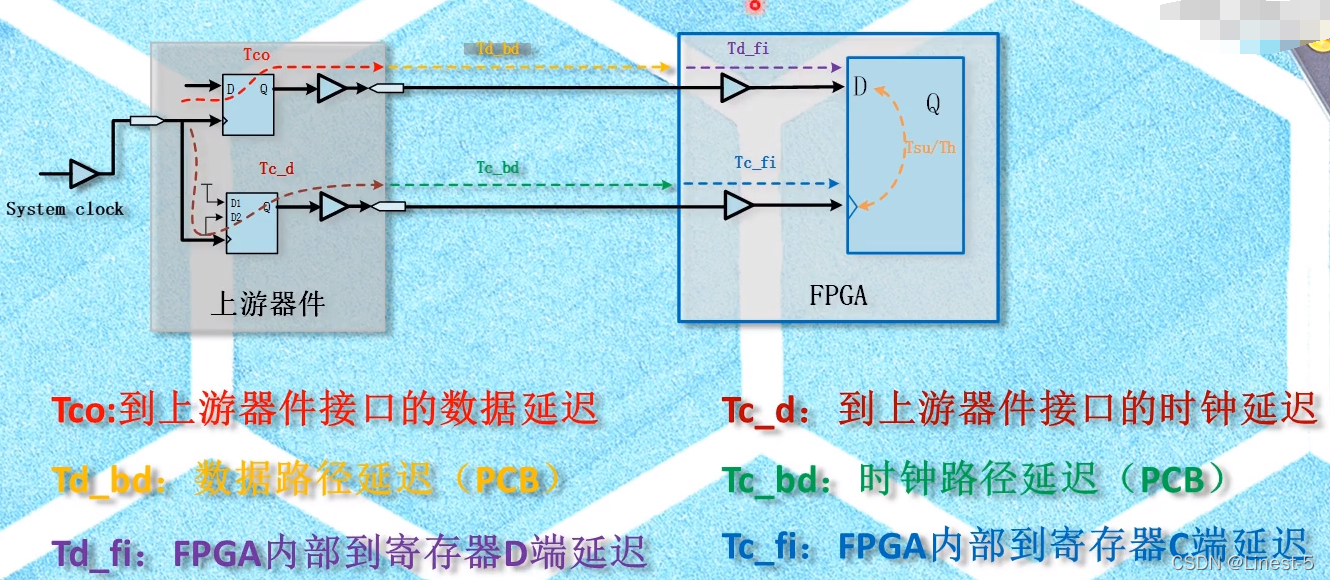

FPGA中亚稳态【Tsu建立时间】【Th保持时间】【Tmet决断时间】【recovery恢复时间】【removal移除时间】CDC跨时钟域处理及相应的时序约束【set_clock_groups】【set_max_delay】

前两篇文章介绍了什么是亚稳态?以及静态时序分析,但那些终究还是理论,那么在实际工程中,如何分析时序路径呢?如何将理论转到实际呢?

系统抖动是由电源噪声、电路板噪声或系统的任何额外抖动引起的整体抖动,使用set_system_jitter 指令可以对时钟抖动进行约束,举例如下:set_input_jitter [get_clocks -of_objects [get_ports clkin]] 0.1,约束...

内含XILINX关于时序约束的官网文档(英文),以及两份时序约束经典透彻中文教程。

FPGA 设计过程中的不同抽象层级:其中最底层的抽象(结构性的)涉及到对底层硬件单元直接的例化,比如逻辑门,甚至是更 底层的 LUT 或者触发器。设计者更常用的是在“寄存器传输级(Register Transfer Level,RTL)”...

通过Quartu自带例程fir_filter进行学习如何使用Timing Analyzer进行时序分析与约束。

Xilinx-ISE辅助设计工具的中文使用说明,包括IP核生成器,布局布线器,FPGA底层编辑器,时序分析器,集成化逻辑分析工具,功率分析工具

FPGA中的时序分析与约束设置

标签: 硬件开发

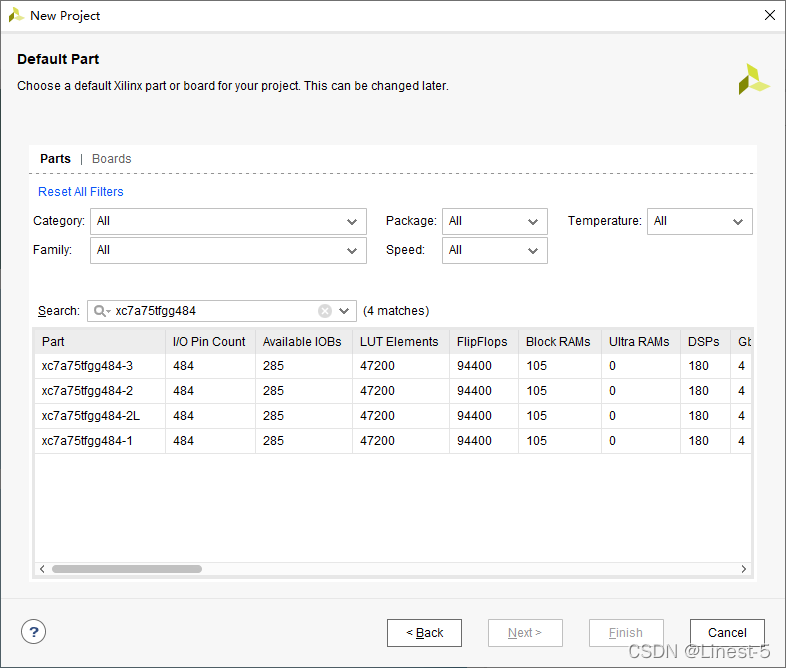

FPGA概述 ## 1.1 FPGA基本原理介绍 FPGA(Field-Programmable Gate Array)是可编程逻辑门阵列,是一种广泛应用于数字电路设计的集成电路。它由海量的可编程逻辑单元(FPGA片上资源),可编程连线(可实现任意...

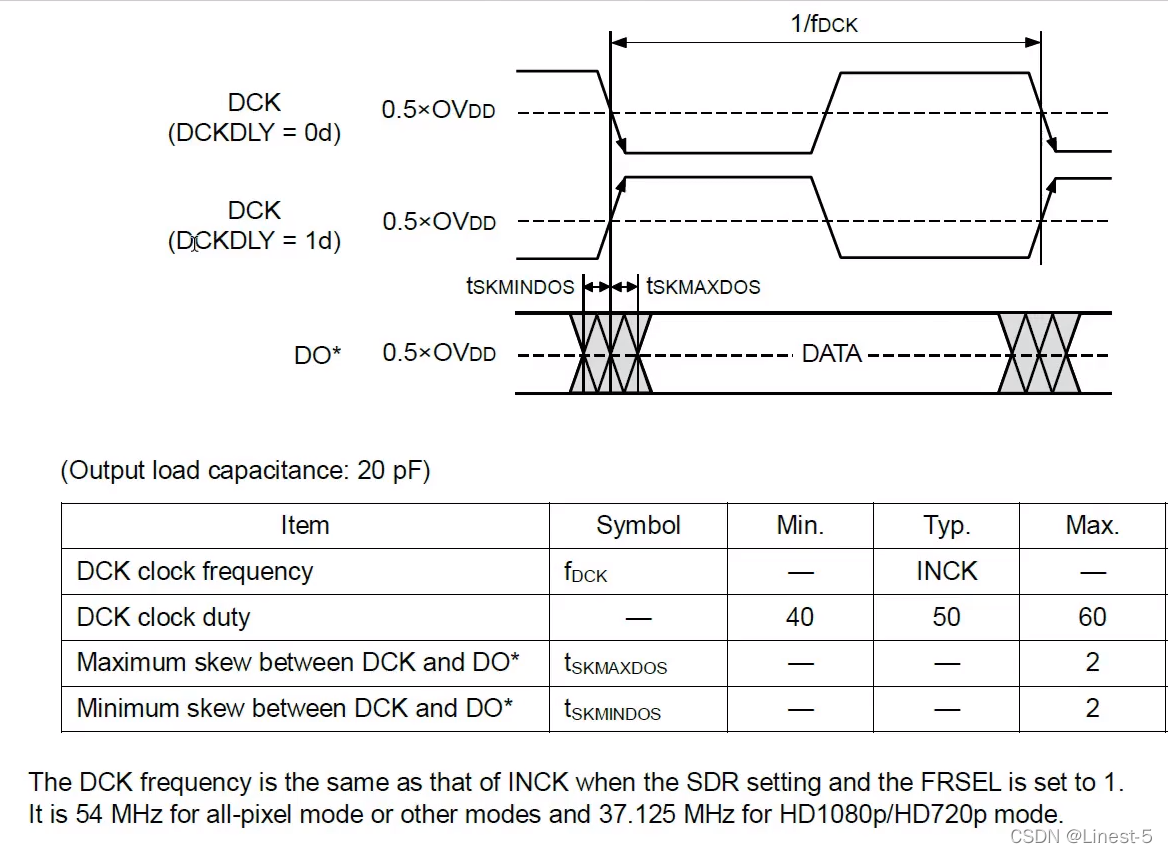

Xilinx FPGA 编程技巧之常用时序约束详解 基本的约束方法 为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为: 输入路径(Input Path),使用输入约束 ...

为帮助 FPGA设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现FPGA 设计的最优结果。何为时序约束?为保证设计的成功,设计人员必须确保设计能在特定时限内完成指定任务。要实现这个目的,...

采用FPGA IO模拟HDMI用来显示图像,对rgb2dvi的IP核的测试,此例中的显示时序都是由PL中产生的,无法灵活更改分辨率,行场同步,之后会用xilinx自带的VTC的IP核,专门产生时序控制时序。

XILINX FPGA时序约束教程。时序约束一共包含以下几个步骤:时钟约束、IO约束以及时序例外。

xilinx时序约束培训教材,大家都知道时序约束对于FPGA开发的重要性,希望这份文档对大家有所帮助。

手册内容为解决FPGA时序不收敛的详细步骤,涵盖从代码到综合整个流程,并给出了指导意见及时序查看方法,此方法为xilinx的FAE推荐。

32个相关文档,都是从网上整理搜集到的,包括时序约束的基本讲解资料,以及altera和xilinx公司的时序约束相关文档

推荐文章

- YOLO V8车辆行人识别_yolov8 无法识别路边行人-程序员宅基地

- jpa mysql分页_Spring Boot之JPA分页-程序员宅基地

- win10打印图片中间空白以及选择打印机预览重启_win10更新后打印图片中间空白-程序员宅基地

- 【加密】SHA256加盐加密_sha256随机盐加密-程序员宅基地

- cordys 启动流程_cordys服务重启-程序员宅基地

- net中 DLL、GAC-程序员宅基地

- (一看就会)Visual Studio设置字体大小_visual studio怎么调整字体大小-程序员宅基地

- Linux中如何读写硬盘(或Virtual Disk)上指定物理扇区_dd写入确定扇区-程序员宅基地

- python【力扣LeetCode算法题库】面试题 17.16- 按摩师(DP)_一个有名的讲师,预约一小时为单位,每次预约服务之间要有休息时间,给定一个预约请-程序员宅基地

- 进制的转换技巧_10111100b转换为十进制-程序员宅基地